Computer chips: Building upward safely

Greater numbers of ever-smaller components are required to fit on computer chips to meet the ongoing demands of miniaturizing electronic devices. Consequently, computer chips are becoming increasingly crowded.

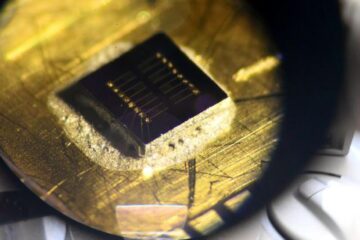

Designers of electronic architectures have therefore followed the lead of urban planners and started to build upward. In so-called ‘three-dimensional (3D) packages’, for example, several flat, two-dimensional chips can be stacked on top of each other using vertical joints.

Controlling the properties of these complex structures is no easy task, as many factors come into play during production. Faxing Che and Hongyu Li and co-workers from the A*STAR Institute of Microelectronics, Singapore, have now developed a powerful modeling method that allows large-scale simulations — and optimization — of the fabrication process, which provides welcome assistance to designers.

Among the challenges of producing tightly packed computer chips is the need to prevent warpage of the underlying silicon wafer as electronics components are stacked on it. Warpage leads to a number of unwanted effects. “Strong warpage can cause wafer breakage, it makes tight packing more difficult and some processing machines cannot handle high-warpage wafers,” explains Li. The degree of warpage depends on many design and process parameters, and optimizing the procedure experimentally is time-consuming and costly.

Using their computer model, Che and Li studied a wide range of parameters that influence the warpage of an 8-inch diameter silicon wafer. They focused, in particular, on how a silicon substrate responds to the deposition of layers of copper — through which electrical currents eventually flow. “This is the first time that a model has been able to predict warpage [at] the level of the entire wafer,” says Li. Moreover, the stress on the wafer can be determined accurately. The calculated values agreed well with experimental data. Importantly, with the computer simulations, the researchers could explore regimes that cannot be easily studied experimentally, such as how the depth of the connections between layers influences wafer warpage.

The next goal is to simulate even larger wafers with variable connection sizes, explains Li. “Today, there are two industry standards for 3D packaging applications, 8-inch and 12-inch wafers, but the latter are becoming increasingly important,” she says. The team’s model is applicable to these larger wafers, too, but it requires optimization. Currently, Che, Li and their co-workers are collecting warpage and stress data for 12-inch wafers. They will use these data for developing their model further, according to Li.

The A*STAR-affiliated researchers contributing to this research are from the Institute of Microelectronics

Journal information

Che, F.-X. X., Li, H. Y., Zhang, X. W., Gao, S. & Teo, K. H. Development of wafer-level warpage and stress modeling methodology and its application in process optimization for TSV wafers. IEEE Transactions on Components, Packaging and Manufacturing Technology 2, 944–955 (2012)

Media Contact

All latest news from the category: Information Technology

Here you can find a summary of innovations in the fields of information and data processing and up-to-date developments on IT equipment and hardware.

This area covers topics such as IT services, IT architectures, IT management and telecommunications.

Newest articles

Sea slugs inspire highly stretchable biomedical sensor

USC Viterbi School of Engineering researcher Hangbo Zhao presents findings on highly stretchable and customizable microneedles for application in fields including neuroscience, tissue engineering, and wearable bioelectronics. The revolution in…

Twisting and binding matter waves with photons in a cavity

Precisely measuring the energy states of individual atoms has been a historical challenge for physicists due to atomic recoil. When an atom interacts with a photon, the atom “recoils” in…

Nanotubes, nanoparticles, and antibodies detect tiny amounts of fentanyl

New sensor is six orders of magnitude more sensitive than the next best thing. A research team at Pitt led by Alexander Star, a chemistry professor in the Kenneth P. Dietrich…