Driving nanoscale microelectronics production

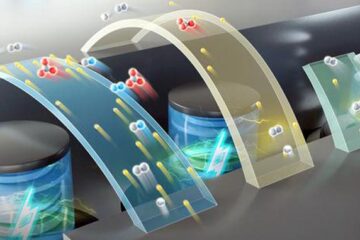

Silicon wafer-based complementary metal oxide semiconductor (CMOS) technology dominates IC manufacture. Its energy efficiency will continue to make it the technology of choice over the next decade for fabrication of microprocessor and memory chips, as well as for application-specific ICs (ASICs) and complete systems-on-chip (SoCs) devices.

Improving performance

The size of the smallest electronic circuit element has long been expressed in microns, but continuous technology revolution means circuit dimensions are now less than 100 nanometre or 1/10th of a micron – leading to the use of ‘nanoelectronics’ rather than ‘microelectronics’. The classical laws of physics no longer apply at this level, giving away to ‘quantum’ physics, which can provide a dramatic improvement in chip performance.

Several EUREKA projects are contributing to the development of future nanometer CMOS generations. As a result of MEDEA+ work, 90 nm node technologies are already in industrial production. The 65-nm node is reaching the product prototyping stage and first choices for a 45-nm technology are available with work continuing towards full process integration well in line with the International Technology Roadmap for Semiconductors (ITRS). “In many cases, products had a 100% first-pass success rate, demonstrating design efficiency and optimum use of technology and manufacturing capabilities,” says Guillermo Bomchil of STMicroelectronics. “And the achievements at 90 nm following the end of the MEDEA+ T201 project set the stage for successful 65-nm prototyping from the end of 2005.”

Looking well ahead

Industrial exploitation of 90-nm CMOS industrial technology is possible based on the rules for industrial fabrication developed in the MEDEA+ T201 CMOS logic 0.1 µm project. In the year following the end of T201, 25 submicron circuits were processed at Crolles 2, at the joint Freescale, Philips Semiconductors and STMicroelectronics pilot 300-mm wafer facility at Grenoble in France. These EUREKA projects have set the scene for the future. MEDEA+ T207 65nm CMOS300 involved new substrate materiels as well as multilevel interconnect metallization for 65nm circuit nodes. The 65-nm process has been established with significant yield improvements and reliability specifications and is now ready for the manufacture of prototype customer chips. The chipmaking partners will be sharing their 65-nm cell libraries and IP blocks are confident about the success of the process to be produced from 2008. And EUREKA projects are already being planned to exploit the results of the EU Sixth Framework Programme (FP6) PULLNANO project that is looking further ahead at the needs for 32-/22-nm scale circuitry.

Media Contact

More Information:

http://www.eureka.be/cmosAll latest news from the category: Information Technology

Here you can find a summary of innovations in the fields of information and data processing and up-to-date developments on IT equipment and hardware.

This area covers topics such as IT services, IT architectures, IT management and telecommunications.

Newest articles

High-energy-density aqueous battery based on halogen multi-electron transfer

Traditional non-aqueous lithium-ion batteries have a high energy density, but their safety is compromised due to the flammable organic electrolytes they utilize. Aqueous batteries use water as the solvent for…

First-ever combined heart pump and pig kidney transplant

…gives new hope to patient with terminal illness. Surgeons at NYU Langone Health performed the first-ever combined mechanical heart pump and gene-edited pig kidney transplant surgery in a 54-year-old woman…

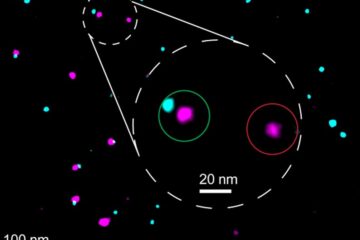

Biophysics: Testing how well biomarkers work

LMU researchers have developed a method to determine how reliably target proteins can be labeled using super-resolution fluorescence microscopy. Modern microscopy techniques make it possible to examine the inner workings…