Towards quicker high level chip design

Competitiveness in the chip design and fabrication sector depends on fast turn-arounds and ever shorter concept-to-product cycles. New hardware design tools based on object-oriented methods should help shorten the design cycle.

The design gap

The complexity of recently available products, such as new 3G mobile phones, camera and PDA combos, is staggering and requires a huge design effort. “There is no doubt that electronic systems of the future are going to be very complex,” says Frank Oppenheimer of the OFFIS Research Institute, Oldenburg, and coordinator of the IST project ODETTE. “The complexity has been on the increase for a decade or so and we expect the trend to continue for the next 10-15 years.”

Chip fabrication technology is improving all the time leading to ever smaller components. This means that chips can be designed to handle greater complexity or, for the same level of complexity, require smaller chip areas and lower power consumption. This opens up many new opportunities.

“The problem is that the design methodologies are, from a technical standpoint, at least ten years old,” comments Oppenheimer. “There is a gap – we call it the design gap – between the methodologies and the technologies available. The tragedy is that these new opportunities cannot be fully exploited with current design methodologies.

“Suppose that, ten years ago, it took a year to design a system. Today, the requirement might be for a system with five times the complexity; using the same methodology, it would take five years to develop. No-one in industry would even consider such a long design cycle,” adds Oppenheimer.

Handling complexity

“When chips were first designed, decades ago, it was carried out at the level of individual transistors and gates,” says Oppenheimer. “Over the years, improvements in design methodology enabled designers to work at a much higher level, for example in terms of the registers and adders found within a microprocessor. This is the RT (Register Transfer) level. These are the basic building blocks within the micro-architecture of application-specific hardware devices (ASICs).”

“Nevertheless, despite this level of complexity, the designer would still be thinking at quite a low level, for instance in terms of basic integer arithmetic or wiring individual components together on the chip. ODETTE enables hardware designers to think in terms of much more abstract data types, perform complex operations with them and provide the means for high-level communication modelling,” says Oppenheimer.

“We have tried to learn from the software domain, which is an area that is more advanced in the handling of complexity,” observes Oppenheimer. “The object-oriented approach has a good track record, and concepts such as Classes and Inheritance are used in the ODETTE methodology. For example, whereas conventional chip design uses the concept of integer arithmetic, the ODETTE methodology would be quite at home working with TCP/IP packets. All the designer would have to do is to model the packet as a Class. We’ve significantly raised the level of abstraction of hardware designs and a spin-off will be to raise the level of productivity.”

Putting theory into practice

There were two dimensions to the ODETTE project. One was to carry out research into the use of object-oriented methods as a means of generating hardware designs. The other was to develop a translator that takes an object-oriented hardware specification and translates it, using hardware synthesis, into something that can be inserted into an industrial design flow for real silicon.

Hardware synthesis based on object-oriented specifications called for the development of new synthesis techniques and tools. This lead to the definition of an extended SystemC/C++ synthesis subset, and a prototype synthesis tool capable of processing it. ODETTE presented a whole new design environment, and many other topics had to be addressed. First class libraries, for example, had to be created to support the hardware synthesis and verification techniques had to be developed, and these greatly benefited from the higher level of abstraction inherent in object-oriented methods.

“The fabrication process involves a number of steps,” says Oppenheimer. “You make a software-like description of the hardware using a language such as VHDL or Verilog. You then use a synthesis tool, which employs a chain of tools to eventually produce something that can be processed on a silicon wafer. The ODETTE implementation can be thought of, in effect, as another element in the chain of tools, which sits on top of all the other tools. Only with tools such as ODETTE will tomorrow’s designers be able to create high-functionality chips with several hundred million transistors.”

“The research work of ODETTE continues in related fields at OFFIS,” says Oppenheimer. “As for the future, we hope the synthesis tool will become commercialised. Part of the methodology, in particular the Language Reference Manual and the simulation library of OSSS, can be downloaded free of charge.”

Contact:

Frank Oppenheimer

Manager System Design Methodology Group

OFFIS – R&D Division Embedded Hardware-/Software-Systems

Escherweg 2

D- 26121 Oldenburg

Germany

Tel: +49-441-9722285

Fax: +49-441-9722282

Email: Frank.Oppenheimer@offis.de

Source: Based on information from ODETTE

Media Contact

All latest news from the category: Information Technology

Here you can find a summary of innovations in the fields of information and data processing and up-to-date developments on IT equipment and hardware.

This area covers topics such as IT services, IT architectures, IT management and telecommunications.

Newest articles

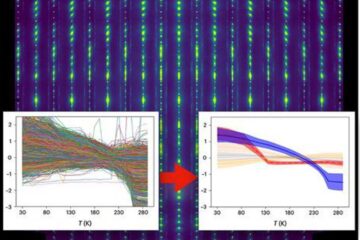

Machine learning algorithm reveals long-theorized glass phase in crystal

Scientists have found evidence of an elusive, glassy phase of matter that emerges when a crystal’s perfect internal pattern is disrupted. X-ray technology and machine learning converge to shed light…

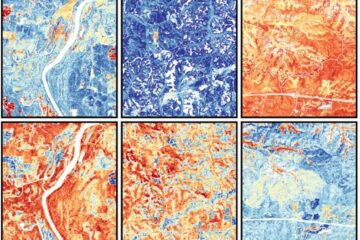

Mapping plant functional diversity from space

HKU ecologists revolutionize ecosystem monitoring with novel field-satellite integration. An international team of researchers, led by Professor Jin WU from the School of Biological Sciences at The University of Hong…

Inverters with constant full load capability

…enable an increase in the performance of electric drives. Overheating components significantly limit the performance of drivetrains in electric vehicles. Inverters in particular are subject to a high thermal load,…