Developing an innovative design platform for future Network-on-Chip

• The NaNoC project aims at developing an innovative design platform for future Network-on-Chip (NoC) based multi-core systems.

• The project is being carried out by a consortium, led by the Parallel Architecture’s Group (GAP) at Technical University of Valencia

Multi-core Systems-on-Chip (SoCs) are becoming ubiquitous in multiple industrial domains, from consumer electronics to automotive, from telecommunications to industrial automation. However, numerous challenges lie ahead, especially regarding the design complexity of such platforms and the physical-level issues as fabrication is further miniaturized. On the other hand, there is today wide consensus on the inherent performance scalability limitations of state-of-the-art interconnect fabrics, ranging from shared busses to bridged busses, all the way to the latest multi-layer communication architectures.

With respect to this, the interconnect fabric, increasingly viewed as the key limiter for effective system integration, is becoming one of the major challenges in the design of on-chip multi-core architectures. To solve this, Networks-on-chip (NoCs) have been proposed as the communication backbone for large-scale integrated systems. They can effectively cope with the productivity gap by providing parallelism through the replication of many identical blocks placed each in a tile of a regular array fabric.

The NaNoC project aims at developing an innovative design platform for future Network-on-Chip (NoC) based multi-core systems. This NaNoC design platform intends to master the design complexity of advanced microelectronic systems by enabling strict component oriented architectural design. A compositional approach to NoC design in future multi-core chips is out of the reach of current design methods and tools due to new design constraints.

Above all, the NaNoC design platform fosters the tight cooperation between system research, circuit design and process development by means of a silicon-aware decision making at each layer of the design hierarchy. In this direction, NaNoC not only provides a cross-layer approach to tackle composability challenges (e.g., physical design techniques for enhanced reliability combined with architecture-level techniques for fault containment), but also defines an exchange format for interoperability between design tools for cross-layer optimization. Interoperability between developed NoC design methods/prototype tools and mainstream design toolflows will also be pursued.

The NaNoC (Nanoscale Silicon-Aware Network-on-Chip Design Platform) started on January 2010, funded by the European Union's Seventh Framework Program (2007-2013). The project is being carried out by a consortium, led by the Parallel Architecture’s Group (GAP) at Technical University of Valencia (Valencia, Spain). About 2.9 million euro (about $4.6 million) of the budget is being provided by European tax payer through the offices of the European Commission and the rest by the project partners including the Technical University of Valencia (Spain), University of Ferrara (Italy), Simula Research Labs (Norway), Infineon Technologies AG (Germany), Teklatech A/S (Denmark), iNoCs SàRL (Switzerland), and Lantiq (Germany).

Project website: http://www.nanoc-project.eu

Luis Zurano Conches

Science Journalist

Universidad Politécnica de Valencia

actualidadi+d@ctt.upv.es

647 422 347

Media Contact

All latest news from the category: Information Technology

Here you can find a summary of innovations in the fields of information and data processing and up-to-date developments on IT equipment and hardware.

This area covers topics such as IT services, IT architectures, IT management and telecommunications.

Newest articles

Properties of new materials for microchips

… can now be measured well. Reseachers of Delft University of Technology demonstrated measuring performance properties of ultrathin silicon membranes. Making ever smaller and more powerful chips requires new ultrathin…

Floating solar’s potential

… to support sustainable development by addressing climate, water, and energy goals holistically. A new study published this week in Nature Energy raises the potential for floating solar photovoltaics (FPV)…

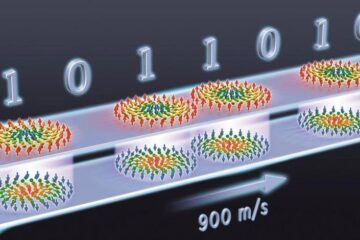

Skyrmions move at record speeds

… a step towards the computing of the future. An international research team led by scientists from the CNRS1 has discovered that the magnetic nanobubbles2 known as skyrmions can be…